# Materials for heterogeneous integration

Madhavan Swaminathan\*, Mohan Kathaperumal, Kyoung-sik Moon, Himani Sharma, Prahalad Murali, and Siddharth Ravichandran

Emerging artificial intelligence (Al) applications require dense connectivity between integrated circuit (IC) chips to enable high-speed computations. Heterogeneous integration (HI) using advanced packaging is being viewed as a critical enabling technology for supporting Al applications. Such highly integrated systems require a multitude of materials to support electrical, mechanical, thermal, and chemical properties. In addition, these materials need to be compatible with packaging processes to ensure compatibility with low-cost manufacturing solutions. The inter-play between the various engineering domains makes the selection of materials, their processability, and compatibility extremely complex. In this article, we investigate the future in terms of the requirements posed by materials for HI and survey the past and present work in this area.

#### Introduction

The proliferation of artificial intelligence (AI) applications has increased the demand for compute performance and memory capacity. This is coming at a time when the semiconductor industry is facing challenges associated with slowing down of Moore's law. Over the last five decades, Moore's Law has enabled the scaling and integration of compute, memory, and other functionalities on a single silicon chip by increasing transistor density on-chip, while keeping the cost per transistor low. This approach known as system-on-chip (SoC) integrates many functions of the system into a single chip. However, with the slowing down of Moore's Law, the cost of large SoCs has increased exponentially due to two main reasons: (1) the cost/ mm<sup>2</sup> of transistors in advanced technology nodes has continued to increase due to increase in technology complexity, and (2) yields have reduced for larger SoCs as we reach the limits of the reticle field. In addition, future electronics is requiring the integration of several IP blocks that may not require the same technology nodes for achieving optimum performance. These limitations and requirements are leaning toward a more cost-effective on-package heterogeneous integration approach to support the growing needs of AI hardware that we refer to here as system-on-package (SoP). Heterogeneous Integration refers to the integration of separately manufactured components into a higher-level assembly that, in the aggregate, provides enhanced functionality and improved operating characteristics. <sup>1</sup>

Two fundamental architectures are currently being pursued by both industry and academia for AI applications referred to as near memory processor (NMP) and processor in memory (PIM). Integration of the CPU, GPU, and high-bandwidth memory (HBM) on a single package, also called an interposer using 2D or 3D connectivity falls under the category of NMP. A better approach is to directly perform computation inside memory, referred to as processor-in-memory (PIM) where the memory array is re-purposed for computation thereby realizing

Madhavan Swaminathan, School of Electrical and Computer Engineering, 3D Systems Packaging Research Center, USA and School of Materials Science and Engineering, Georgia Institute of Technology, USA; madhavan.swaminathan@ece.gatech.edu

Mohan Kathaperumal, School of Electrical and Computer Engineering, 3D Systems Packaging Research Center, Georgia Institute of Technology, USA; kmohan@ece.gatech.edu

Kyoung-sik Moon, School of Materials Science and Engineering, 3D Systems Packaging Research Center, Georgia Institute of Technology, USA; Jack.moon@gatech.edu Himani Sharma, School of Materials Science and Engineering, 3D Systems Packaging Research Center, Georgia Institute of Technology, USA; himani.sharma@mse.gatech.edu

Prahalad Murali, School of Materials Science and Engineering, 3D Systems Packaging Research Center, Georgia Institute of Technology, USA; prahalad.murali@gatech.edu

Siddharth Ravichandran, School of Electrical and Computer Engineering, 3D Systems Packaging Research Center, Georgia Institute of Technology, USA; Siddharth.ravichandran@gatech.edu \*Corresponding author

doi:10.1557/s43577-021-00212-2

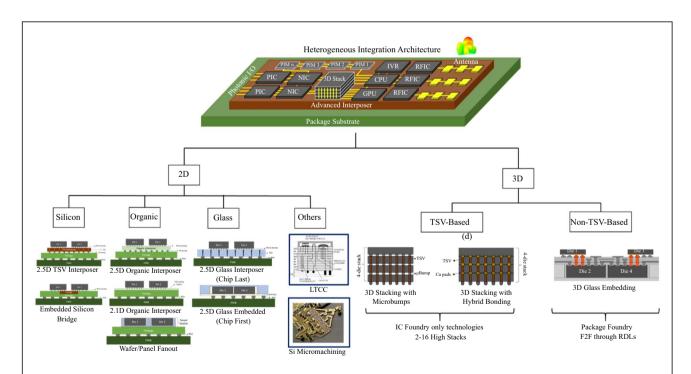

massive parallelism and almost nullifying data movement.<sup>2</sup> The fundamental differences between these two approaches relate to three important metrics namely, memory capacity, latency (or delay), and energy consumption. As applications emerge in AI, there is a need for continuous interaction and learning from the environment. This requires neuro-evolution in hardware, where inferences need to be supported in the absence of pre-trained deep neural networks (DNN) and labeled datasets. For such architectures, data movement with low energy per bit (EPB) and high-bandwidth density become critical. As AI architectures become more prevalent, there will be a need for integrating additional chips from domains such as analog, radio frequency (RF), sensing, and photonics along with the compute domains from different process nodes, leading to extreme heterogeneity as shown in Figure 1.3

The HI architectures can be implemented using a variety of packaging platforms broadly classified into 2D and 3D approaches (Figure 1). In the 2D approach, bare dies (or chiplets) are placed side by side and connected to each other through interconnections in the package substrate. Interposers can be viewed as a large chip consisting of several smaller chiplets connected to each other that also serves the role of a conduit between the dies on top and package substrate at the bottom. In contrast, in the 3D approach, dies are vertically stacked and connected to each other using through-silicon

vias (TSVs) and other chip bonding technologies along with non-TSV-based solutions. A variety of materials and package constructions are possible in the 2D and 3D approaches, where these embodiments differ from each other in bandwidth density, energy per bit (EPB), power delivery efficiency  $(\eta)$ , and thermal design power (TDP). These represent important metrics that need to be addressed as we progress towards extreme heterogeneity for future AI systems. In the following sections, we investigate the role of materials in supporting these metrics.

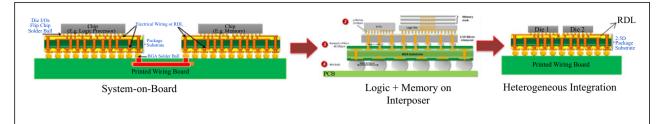

# Materials for meeting bandwidth density and EPB metrics

Bandwidth density refers to the number of bits transmitted and received between dies per mm (millimeter) for 2D and per mm<sup>2</sup> for 3D. This is largely dictated by the wiring density, wire length, and signaling data rate on each wire. Today, for 2.5D interposers, the bandwidth density is in the range 500-5000 Gbps/mm, while for 3D, the range is 1-5 Tbps/ mm<sup>2</sup>. With a trend towards big data, there is a continuous need to increase the bandwidth density even further through miniaturization, as shown in Figure 2. The wiring density is determined not only by the photosensitive materials (photoresists or photo-imageable) used but also the lithographic process and tooling required for patterning and etching. The ability

Figure 1. HI Architecture supporting compute, communication, sensing and control functionality (top), and Advanced Packaging Solutions using 2D and 3D approaches (bottom). Two-dimensional solutions represent high-density packaging also called 2.5D. Silicon, organics, glass, and ceramics are the substrate materials of choice for 2D integration. Through-silicon via (TSV) interposer, embedded silicon bridge (EMIB), organic interposer, wafer & panel level fanout, glass interposer (chip last/first), low temperature co-fired ceramic (LTCC), and micromachining are examples of 2D approaches. Similarly, TSV and non-TSV-based stacking using microbumps, and hybrid bonding are examples of 3D integration. With 3D integration, either an integrated circuit (IC) or package foundry can be used for manufacturing based on the construction. RDLs redistribution wiring layers.

Figure 2. Heterogeneous integration requires high wiring density with fine pitch lines and spaces in the redistribution wiring layers (RDLs).

to communicate between dies with high-bandwidth density at low EPB requires low wire capacitance, which translates to shorter wires between dies and low dielectric constant materials. The integration of ultra-low  $D_{\rm k}$  (ULK) materials in the redistribution wiring layers (RDLs) of the package therefore becomes a major requirement.

There are several material candidates that have low dielectric constant that have been developed for applications using back-end-of-the-line (BEOL) processes. <sup>4-7</sup> **Table I** lists the polymers used by industry that have a dielectric constant ( $D_k$ ) of 3 or more. This is primarily since ULK materials ( $D_k < 2.5$ ) need to be qualified based on several different properties of polymers. Table I also shows the properties of the polymer dielectrics that are needed in systems for AI and high-performance computing (HPC) applications.

A critical property of ULK materials for packaging applications is their coefficient of thermal expansion (CTE). For the package to be reliable, the ULK dielectric material should exhibit a CTE close to that of the copper metal layer. For ULK materials, this is hard to achieve owing to the inability to use filler particles which increases the dielectric permittivity of the polymer. The filler particles used are typically  $SiO_2(D_k=3.9)$ , and since the fillers need to be loaded in high volume/weight% compared to neat polymer dielectrics such as fluorinated polymers, they do not help reduce the  $D_k$  value. The presence of added fillers in polymer dielectrics used as build-up layers also becomes a bottleneck for scaling of microvias. To achieve highest wiring density with fine lines and spaces, the diameter of the microvias should be comparable to the line width and spacing. The ULK polymers containing highly fluorinated monomers create additional challenges in the form of reduced adhesion of both polymer on copper and copper on polymer. This is a formidable task since it requires careful selection of adhesion promoters and surface treatments for achieving reliability of the fabricated structures by overcoming delamination during environmental and accelerated aging studies. This is an area of ongoing research at panel scale for packaging. Additional challenges such as plating and seed layer etching arise while scaling to panel level processes since semi-additive processing (SAP) is the preferred method for RDL fabrication.

Aside from low dielectric permittivity materials, there is also a renewed interest in photo-imageable dielectrics (PID)

particularly for high-density interconnects. This interest arises from two aspects: (1) number of steps used in the SAP process can be reduced by employing PIDs as the need for photoresists is eliminated, and (2) PIDs can impart better resolution in terms of fine line patterning.<sup>8</sup> However, all the currently available PIDs have a dielectric constant >2.5 which represents a major roadblock for achieving high density, low capacitance, and high aspect ratio fine line interconnects.

The research work being pursued at the Packaging Research Center (PRC)^{2,9-17} is directed towards achieving very high wiring density with fine lines/spaces (<1  $\mu m$ ) that include dielectric build-up layers with a dielectric constant <2.5 and polymer microvias with diameter <2  $\mu m$ . This research is also directed towards using the SAP process that is compatible with panel-scale processes and is essential for fabricating large body size interposers. Furthermore, it is equally important to develop panel-scale processes using ultra-thin dielectrics with high surface planarity to support fine lines and spaces. The surface planarity of the polymer dielectric becomes critical when the line width and space are less than 2  $\mu m$  as thickness variations over the length of the panel will affect the yield of the fine line features.

# Materials for increasing power delivery efficiency

The power delivery efficiency  $\eta$  represents the ratio of the power delivered to the die to the power delivered to the voltage regulator (VR). The efficiencies are typically in the range 75-80% for high-performance computer applications. These efficiencies can be increased by either decreasing the effective resistance between the VR and die or/and integrating highvoltage conversion ratio regulators near the die on the same package. 18 For such integrated voltage regulators (IVR), the inductor serves as an energy storage element by delivering current to the output. The key performance metrics which are used to judge the performance of inductors are its energy density, quality factor, and saturation characteristics. This requires the integration of new magnetic materials capable of highfrequency operation. Another key aspect of power delivery to the chip is managing the voltage drop that comes from the parasitic loop inductance in the power delivery network (PDN) during events of spike in load current of the chip. Decoupling

| ULK dielectrics                                                                                                                                                                          |                         | Thickness Dry film vs liquid; lamination vs spin-coating, other casting methods | Copper to polymer;<br>copper to substrate<br>Surface roughness;<br>filler size planariza-<br>tion: fly cut, CMP<br>Polymer to copper;<br>polymer to substrate | Surface roughness;<br>filler size planariza-<br>tion: fly cut, CMP | Warpage of films;<br>residual stress;<br>elongation to break | Low CTE Close to copper (17–18 ppm/*k) or substrates such as glass (3–9 ppm/*k); silicon (3 ppm/*k); organics such as FR-4 (E-glass filled; 16–20 ppm/*k) | Moisture absorption<br>Leakage current<br>Electrochemical<br>migration<br>Barrier layer materials |                    |                    |                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------|--------------------|-------------------|

| Table I. (Left) dielectrics currently used in some of the commercially available as well as advanced packaging solutions ULK;5-15,77 (right) key properties required for ULK dielectrics | Key Properties          | Processability                                                                  | Adhesion to copper<br>plated substrates                                                                                                                       | Surface planarity of films                                         | Mechanical reliability                                       | Coefficient of thermal expansion (CTE)                                                                                                                    | Electrical reliability                                                                            |                    |                    |                   |

|                                                                                                                                                                                          | Type of package         | Interposer (panel)                                                              | Fanout (wafer)                                                                                                                                                | Fanout (panel)                                                     | Interposer (wafer)                                           | Fanout (panel)                                                                                                                                            | Interposer (wafer)                                                                                | Interposer (panel) | Interposer (panel) | Interposer(panel) |

|                                                                                                                                                                                          | Process                 | SAP                                                                             | SAP                                                                                                                                                           | RDL first                                                          | BEOL                                                         | BEOL                                                                                                                                                      | BEOL                                                                                              | SAP                | SAP                | Embedded trench   |

|                                                                                                                                                                                          | Thickness of Dielectric | > 10 µm                                                                         | > 15 µm                                                                                                                                                       | × 5 μm                                                             | >2 µm                                                        | >5 µm                                                                                                                                                     | >2 µm                                                                                             | ı                  | ı                  | ₩ < 3 mm          |

|                                                                                                                                                                                          | RDL, line/space         | 2/2 µm (R&D)                                                                    | 2/2 µm (R&D)                                                                                                                                                  | 2/2 µm (R&D)                                                       | < 2/2 µm (R&D)                                               | 2.2 µm (product)                                                                                                                                          | < 0.5 µm (product)                                                                                | 6/6 µm (product)   | 6/6 µm (R&D)       | 2/2 µm (R&D)      |

|                                                                                                                                                                                          | $D_k$                   | 3.0–3.5                                                                         | 3.0–3.6                                                                                                                                                       | 3.1                                                                | 4                                                            | 4                                                                                                                                                         | m                                                                                                 | ı                  | >3.0               | 3.0               |

|                                                                                                                                                                                          | Material                | Photosensitive-resin                                                            | Polyimide (PI)                                                                                                                                                | Polybenzoxazole (PBO)                                              | Silicon oxide                                                | Silicon oxide                                                                                                                                             | Silicon oxide                                                                                     | ı                  | I                  | Epoxy             |

| Table I. (Left)                                                                                                                                                                          |                         | Shinko's organic interposer (i-TH0P)                                            | Amkor (SWIFT)                                                                                                                                                 | SEMCO                                                              | Amkor (SLIM)                                                 | Intel EMIB                                                                                                                                                | Xilinx                                                                                            | Cisco              | Kyocera APX        | Glass Interposer  |

capacitors at multiple stages of the PDN keep the impedance spikes below tolerance across broad frequency ranges. However, the size, equivalent series resistance (ESR) and series inductance (ESL), and cost of the decoupling capacitor play a crucial role in determining the quality of power delivery, especially with the number of power rails being more than 50 in modern computing applications. <sup>18</sup>

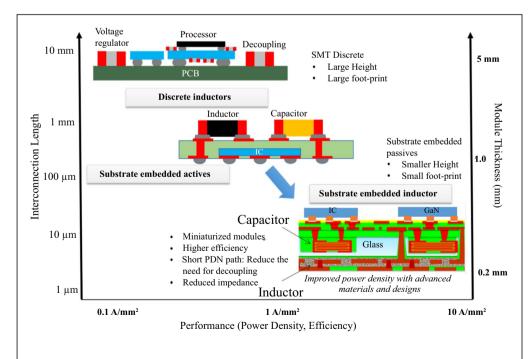

The trend for power delivery in HI is shown in **Figure 3**, where the objective is to maximize the power density while reducing interconnect length and module thickness. This requires the integration of two critical components namely, inductor and capacitor. Miniaturization of these components along with integration beneath the die shadow requires high-permeability magnetic materials and high  $D_{\rm k}$  materials, respectively, as shown in Figure 3.

### **Magnetic materials**

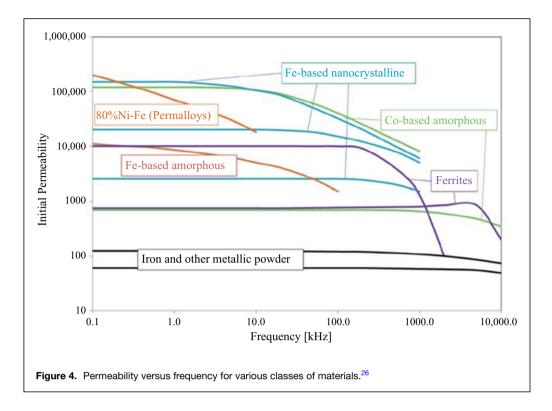

Magnetic materials are chosen based on, (1) permeability at the desired operating frequency, (2) ferromagnetic resonance frequency (FMR), (3) loss tangent (ratio of real part of permeability ( $\mu$ ') to complex part of permeability ( $\mu$ ")), and (4) saturation magnetization. Magnetic materials are usually used in the form of powdered cores, metal polymer composites, and thin films that are easily processable. Factors influencing magnetic properties of the material are (1) alloy composition, (2) particle size, (3) particle shape, <sup>19</sup> (4) grain size, (5) grain orientation, and (6) process conditions. Alloys with varying percentages of metal constituents have different properties that can be exploited based on the application. When the grain sizes are large enough such that grain boundaries are at a

minimum (e.g., Hitachi Metglas®), such materials have good soft magnetic properties including low coercivity, low loss, and high-permeability, which are of importance for a variety of applications.

Ferrites are a class of materials that are used when the required frequency of operation is around 100s of kHz. Ferrites typically have lower saturation magnetization and low permeability. Although with some modifications, ferrites can be extended to applications in the few 10s of MHz range, they are not preferred when compared to metal alloys which are the materials of choice in the MHz range. Soft magnetic alloys like Fe–Si have higher permeability but use of these materials at higher frequencies leads to significant losses, since the permeability of these materials increases depending on the weight percentage of Si. With addition of silicon, the permeability increases to its highest value at 6.5 wt% of Si (Fe93.5Si6.5) and decreases upon continued addition of more silicon.<sup>20</sup> Other soft magnetic materials include alloys of nickel, zinc, and cobalt which typically have high magnetization saturation and high permeability. However, due to their high conductivity, they generate eddy currents at high frequencies. This has been addressed by use of low conductivity elements like boron, phosphorus, and oxygen which help in reducing the eddy current losses.<sup>21</sup> The presence of oxide/phosphate on metal particles keeps the eddy current losses low by reducing contact between adjacent particles thereby reducing eddy current loop, which, however, reduces the permeability as well. Metal polymer composites exhibit better properties as the metal particles are dispersed in a polymer matrix which prevent longer eddy current paths. The permeability of polymer

> composites is influenced by the amount of loading and shape of the particles. For example, flake-shaped particles have higher x-y plane permeability when compared to spherical ones. Due to this reason, metal polymer composite sheets with metallic particle flakes are being investigated actively as possible candidates for package-embedded inductors.

Size of the metallic particles in polymer composites plays a significant role as the particle size is proportional to the eddy current losses. Mechanical deformation during

**Figure 3.** Trend for power delivery using embedded inductors and capacitors using high-permeability magnetic materials and high-permittivity dielectric materials. SMT, surface mount technology; PDN, power delivery network; IC, integrated circuit.

processing has a detrimental effect on the soft magnetic properties as well.<sup>22</sup> Usually, materials used at RF frequencies have been fabricated through low throughput methods such as sputtering.<sup>23–25</sup> Although thin films have high FMR, they are limited by their current handling capabilities which limit their application in power delivery.

Figure 4 shows the operating frequency range for various classes of magnetic materials. In the recent past, materials exhibiting high-frequency stability have been demonstrated. Trade-offs between frequency stability, permeability, and losses must be considered when designing and synthesizing magnetic materials.

The permeability for magnetic materials reported in the literature is in the range 5–1000, with magnetic loss tangent of 0.01-1 and FMR of 1-100 MHz. For composite materials, an important exercise is to optimize the volume fraction of the metal particles thereby increasing FMR frequency while reducing magnetic loss tangent, with a reasonable permeability. As we move towards higher voltage IVRs using stacked FinFETs or GaN-based devices, the target switching frequency is in the 5–50 MHz range. This allows for a relatively small inductor while keeping switching losses manageable. Based on a trade-off between saturation current, inductance density, and DC resistance, the required properties of the magnetic material can be derived using the Lorentz and Landau-Lifshitz-Gilbert equation. <sup>18,27</sup> As an example, for a 48 V/1 V conversion @ 10 MHz with 90% efficiency, the magnetic material should have a permeability of  $\sim 90$ , loss tangent less than 0.033 at 10 MHz and stability up to 50 MHz.<sup>28</sup> However, most commercially available high-permeability materials have a loss tangent that is unacceptably high at frequencies of 10 MHz or higher, which becomes a bottleneck.

# Dielectric (high D<sub>k</sub>) materials

There is a demand for capacitors with ultra-high volumetric densities in smaller form-factors. Additionally, to minimize the power wastage in granular power management systems, thinner capacitors are needed that determine the overall efficiency.

Industry is making use of embedded discrete capacitors in their processor packages. The low

inductance provided by placing capacitors closer to the die is desirable for supporting high-bandwidth processing. Intel demonstrated the impedance benefits of embedding capacitors in the substrate, directly beneath the die, in addition to surface-mount capacitors on the opposite sides of the substrate. A significant drop in impedance was observed from 5 to 300 MHz, especially around the power supply spike at 130 MHz, which exists when decoupling capacitors are placed far from the die.<sup>29</sup>

Multilayered co-fired ceramic capacitors (MLCCs) provide high volumetric capacitance density at low cost and are available for board-level assembly using standard surface-mount technologies (SMTs). More recent advances in materials have led to high-permittivity dielectrics for miniaturization by adding ferroelectric fillers to dielectric laminates to increase the dielectric constant. In the early 2000s, Motorola developed a photo dielectric with a permittivity of 20-22 using this concept.<sup>30</sup> Similarly, 3M has developed embeddable laminate capacitor with copper thickness down to 6 µm that can achieve up to 6.2 nF/cm<sup>2</sup>.<sup>29</sup> Although inorganic materials such as BaTiO<sub>3</sub> and SrTiO<sub>3</sub> provide very high dielectric constants ~2500, owing to the difficulty in processing these materials, package integration becomes difficult. However, by using polymer nanocomposites consisting of barium titanate nanoparticles (30–50 nm diameter) with suitable surface modifiers such as phosphonic acids,  $D_k$  between 20 and 50 can be attained with low temperature processing in thin films.<sup>31</sup> Organically modified sol-gel material with  $D_k \sim 20^{32}$  have also been reported which can be processed at temperatures <120°C with a wide range of film thicknesses.

While integrated ferroelectric ceramics are an attractive option for higher capacitance densities, ceramic capacitors require high-temperature processing due to the solid-state diffusion reaction between BaCO<sub>3</sub> and TiO<sub>2</sub> particles that takes place at 950–1200°C.<sup>33</sup> These firing temperatures are incompatible with the rest of the package process (exception being LTCC) and, thus, are primarily used as discrete components formed separately. To form ceramic capacitors directly onchip, lower processing temperatures are required. Much effort has been focused on using sol–gel processing to achieve this, which only requires a final high-temperature annealing step.

Silicon-integrated trench capacitors are much more compatible with on-chip decoupling than ceramic capacitors. Therefore, developmental work has focused on enhancing their capacitance to compete with ceramics. This is largely enabled by advanced etching and deposition processes. For example, Apple's A10 processor used land-side decoupling with silicon deep-trench capacitors from TSMC.<sup>34</sup> The insertable silicon chip capacitors can be embedded into the package, as Apple did in their integrated DRAM-logic module. The capacitors can attain up to 500 nF/mm<sup>2</sup> down to 100 µm thickness. Since the capacitors are based on paraelectric silicon dioxide dielectric, they have superior voltage and temperature coefficients of capacitance and are available up to 4.5 V rating.

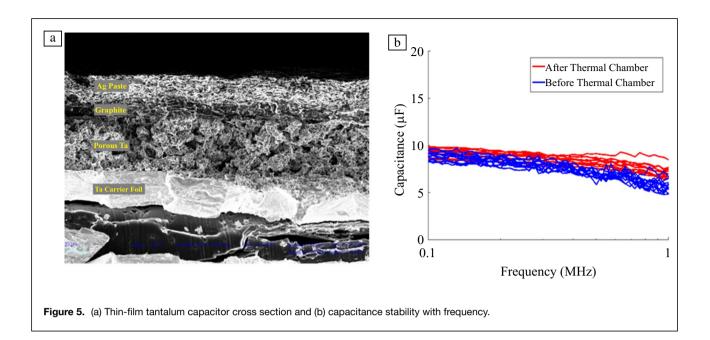

Electrolytic capacitors have potential to provide some of the highest volumetric densities owing to their ultra-high surface areas and thin dielectrics. However, they are generally formed as pressed pellets or wound sheets, which make them bulky. A new design that uses a panel scalable, singleetched aluminum sheet has been developed to overcome this challenge.<sup>35</sup> A combination of high surface area from etched Al sheet and conducting polymer cathode layers yields high capacitance density without the high-temperature constraints. These capacitors can then be released on the chip using a foiltransfer process. PRC has demonstrated embeddable tantalum capacitors of  $\sim 100 \, \mu m$  thickness<sup>36</sup> with a density  $> 2 \, \mu F/$ mm<sup>2</sup> at 1 kHz and  $> 1 \mu F/mm^2$  at 1 MHz. The tantalum nanoparticle anode is printed on a tantalum carrier foil as a paste before sintering. The carrier foil with capacitor layer is then transferred onto the wafer or package. A cross section of the thin-film capacitor is shown in **Figure 5**.

The increase in capacitance density of silicon capacitors like MIM capacitors have made them good candidates for filtering the output ripple in high-frequency IVRs. Recent improvements in deep-trench capacitor technology could make them a good candidate for providing sufficient decoupling even down to 10 MHz. One problem with currently available silicon capacitors is their inability to handle high voltages. As we move towards high-voltage IVRs with higher input voltage, we will need high-frequency decoupling for the input rail that can handle higher voltage. One possible alternative to high-voltage silicon capacitors is the development of high-voltage, high-frequency package capacitors such as thin-film capacitors <sup>18,37</sup> and embedded array capacitors. <sup>38</sup>

## Materials for managing thermal design power

The thermal design power (TDP) represents the sustained maximum power that a computing element can support while keeping the die junction temperature below its maximum allowable limit, which is typically around  $100^{\circ}$ C. It is calculated as the ratio between the temperature difference ( $\Delta T$ ) and effective thermal resistance, where  $\Delta T$  is the difference between the die junction and ambient temperatures.

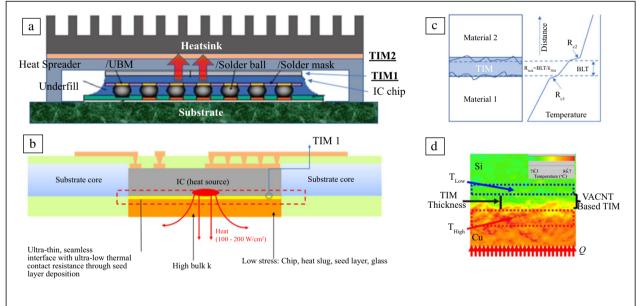

A large contributor towards the effective thermal resistance is the thermal conductivity of thermal interface materials (TIMs). They are used in flip-chip packages and embedded fanout packaging, shown as TIM1 (between die-to-heat spreader) and TIM2 (between heat spreader-to-heatsink) to remove the heat from the top or bottom surface, as shown in **Figure 6**.

In general, TIM is employed for filling the interfaces between thermal components, where microscale point contacts between rough surfaces of the components result in limited contact surface area and reduced thermal channels through the interfaces. Air in the micro-pockets at the interfaces have an adverse impact on interfacial thermal transport due to its poor thermal conductivity (~0.025 W/mK @25°C) which can significantly increase the interfacial thermal resistance. The thermal conduction dramatically degrades while traveling through the interfaces owing to the interfacial thermal resistance, as shown in Figure 6(c), where decreasing bond line thickness (BLT) and increasing thermal conductivity of the filled interface space help mitigate thermal loss via decreased interfacial thermal resistance. The thermal resistance  $(R_{TIM})$  of TIM can be expressed as  $R_{TIM} = BLT/k_{TIM} + R_{c1} + R_{c2}$  where  $k_{TIM}$ is the thermal conductivity of TIM. Along with the thermal conductivity of TIM materials, it is very important to secure the interfaces through mechanical adhesion and thermal coupling for mitigating thermal scattering at these interfaces. In addition, Young's modulus and CTE of TIMs are also critical parameters that determine the thermomechanical reliability of the package along with the pressure requirements for bonding to ensure compatibility with package processes.

In general, various types of TIMs are available, for example, in the form of grease (silicone-based matrix filled with thermal fillers/boron nitride (hexagonal-BN)<sup>40</sup> or alumina-Al<sub>2</sub>O<sub>3</sub>), 41,42 phase change materials (PCM, utilizing latent heat during melting, polyolefin and low Mw polyester), 43-45 gels and adhesives (silicon-nitride<sup>46</sup> or silver-filled epoxy).<sup>47,48</sup> The h-BN and exfoliated h-BN nanosheets (BNNS) have been extensively studied as thermal filler in polymer or ceramic composites with high thermal conductivity and electrical resistivity. 49-62 h-BN is a z-direction stacking structure that uses van der Waals bonding of covalently bonded 2D hexagonal boron-nitrogen (h-BN) atoms, which is very similar to the structure and thermal properties of graphite. For insulating TIMs, alumina filler is used for <4 W/mK while alumina/ h-BN blend or BN filled TIM can reach ~17 W/mK by controlling filler sizes and morphologies. 63 Besides, low loadings

**Figure 6.** (a) and (b) Schematics of flip-chip and embedded package showing die, thermal interface material TIM1, and TIM2 where major heat transport flows upward or downward, (c) schematic of rough surfaces filled with TIM and thermal resistance at the interfaces with BLT, and infrared image of a real interfacial TIM between silicon and copper blocks.<sup>39</sup> BLT, bond line thickness; IC, integrated thickness; VACNT, vertically aligned carbon nanotube.

of aligned BNNS-filled silicone have exhibited 10–12 W/mK, but the higher loading without compromising viscosity can be challenging to achieve.

Carbon allotropes such as multi-walled/single-walled vertically aligned carbon nanotubes (CNTs), <sup>64,65</sup> aligned graphene nanosheets, <sup>66</sup> graphite nanoplates, <sup>67</sup> carbon black, <sup>68</sup> CNT/ metal composite, etc. have recently received much attention for TIM applications due to their exotic thermal conduction

performance via ballistic transport (> 3000 W/mK). In addition to polymeric and metal/carbon composites, metallic TIMs such as solder alloys have been employed in microprocessor cooling because of their high thermal conductivity. In addition, more solutions such as "wet" solder (liquid metal) TIM by using liquid metal such as Ga that is less toxic with a lower vapor pressure than mercury, such as GaIn, GaInSn, and others have been investigated. <sup>69,70</sup>

Among several approaches to TIMs, high thermal conductivity thermal filler loaded adhesive types of TIMs such as silver (429 W/mK),<sup>36</sup> copper (401 W/mK),<sup>71,72</sup> aluminum (~205 W/mK),<sup>73</sup> transient liquid-phase sintering (TLPS),<sup>74,75</sup> and others in thermoset type resins are promising candidates.

Recent developments on TIM have been focusing on the filler/interface engineering to address the limited thermal conductivity of TIM and its interfacial thermal resistance to bonding substrates, including exploitation of nanosilver sintering at low temperatures in the form of dry metal sintering (>70 W/mK) or fusion in polymer (>30 W/mK) (interfacial atomic/grain boundary diffusion induces metallurgical interconnections between nanoparticles to form the thermal paths). <sup>76</sup>

### **Summary and path forward**

AI applications are driven by the ability to communicate between logic and memory with minimum delay. With the trend towards heterogeneous integration, off-chip communications between dies become important where the delay is dictated by the relative permittivity of the dielectric material used. Lowering dielectric constant not only reduces delay but also the EPB. As the future unfolds, dielectric materials with permittivity less than 2.5 are required which are processable as part of a package stack-up that supports fine line width, small spacing, and microvia geometries for supporting large bandwidth density. Hence, the mechanical, chemical, and thermal properties of the material become equally important. The large number of memory-compute operations often causes a power delivery problem, where large currents must be supplied to the dies causing excessive DC drops and AC noise. This can be mitigated using IVRs operating near the die on the same package. Such implementations require highdensity inductors and capacitors embedded in the package, requiring high-permeability magnetic materials and highpermittivity insulating materials. Most magnetic materials are limited by their loss, FMR, and saturation magnetization in the frequency range 1–100 MHz. With high-permittivity materials, a major bottleneck is their ability to withstand high voltages. With most data center implementations having an efficiency in the 75-80% range, any improvements in both magnetic and dielectric materials can have a large impact on energy efficiency. Finally, TIM represents a critical material that is in the heat dissipation path for all dies, and often times becomes the showstopper in our ability to dissipate large heat flux. An ideal TIM would have (1) thermal conductivity better than that of copper that can be directly deposited on the die, and (2) CTE matched with that of the die to ensure reliability.

In this article, we have only focused on four important material systems that are essential for enabling the next generation of AI systems, understanding fully well that there are more materials and interfaces that one needs to address to build highly integrated heterogeneous systems.

### **Conflict of interest**

The authors declare that they have no conflict of interest.

### References

- 1. https://eps.ieee.org/technology/heterogeneous-integration-roadmap/2019-edition.html

- 2. S. Mukhopadhyay, Y. Long, B. Mudassar, C.S. Nair, B.H. DeProspo, H.M. Torun, M. Kathaperumal, V. Smet, D. Kim, S. Yalamanchili, M. Swaminathan, *IBM J. Res. Dev.* (2019). https://doi.org/10.1147/JRD.2019.2947373

- 3. S. Ravichandran, M. Swaminathan, Heterogeneous integration for Al applications: Status & future needs, microwave magazine (under review)

- 4. A. Grill, S.M. Gates, T.E. Ryan, S.V. Nguyen, D. Priyadarshini, *Appl. Phys. Rev.* 1, 011306 (2014)

- 5. A. Grill, J. Vac. Sci. Technol. B 34, 020801 (2016)

- 6. B.D. Hatton, K. Landskron, W.J. Hunks, M.R. Bennett, D. Shukaris, D.D. Perovic, G.A. Ozin, *Mater. Today* **9**(3), 22 (2006)

- 7. L. Wang, C. Liu, S. Shen, M. Xu, X. Liu, *Adv. Ind. Eng. Polym. Res.* **3**, 138 (2020) 8. F. Liu, C. Nair, A. Kubo, T. Ando, H. Lu, R. Zhang, H. Chen, K.S. Lee, V. Sundaram, R.R. Tummala, *2017 IEEE 67th Electronic Components and Technology Conference (ECTC)*

- (Orlando, May 30–June 2, 2017), pp. 2097–2103 9. F. Liu, G. Khurana, R. Zhang, A. Watanabe. B. DeProspo, C. Nair, R. Tummala, M. Swaminathan, *IEEE Trans. Compon. Packaging Manuf. Technol.* **9**, 2016 (2019)

- 10. F. Liu, C. Nair, H. Ito, B.H. DeProspo, S. Ravichandran, H. Akimaru, K. Hasegawa, R. Tummala, *IEEE Trans. Compon. Packaging Manuf. Technol.* **9**, 1426 (2019)

- 11. F. Liu, C. Nair, G. Khurana, A. Watanabe, B.H. DeProspo, A. Kubo, C.P. Lin, T. Makita, N. Watanabe, R.R. Tummala, 2019 IEEE 69th Electronic Components and Technology Conference (ECTC) (Las Vegas, May 28–31, 2019), pp. 924–930

- 12. S. Dwarakanath, P. Markondeya Raj, A. Agarwal D. Okamoto, A. Kubo, F. Liu, M. Kathaperumal, R.R. Tummala, 2019 IEEE 69th Electronic Components and Technology Conference (ECTC) (Las Vegas, May 28–31, 2019), pp. 718–725

- 13. B. DeProspo, A. Momozawa, A. Kubo, C. Nair, V. Rajagoapal, J. Kannan, E. Surillo, F. Liu, M. Kathaperumal, R. Tummala, *2019 IEEE 69th Electronic Components and Technology Conference (ECTC)* (Las Vegas, May 28–31, 2019), pp. 334–339

- 14. F. Liu, R. Zhang, G. Khurana, B.H. DeProspo, R.R. Tummala, M. Swaminathan, *IEEE Trans. Compon. Packaging Manuf. Technol.* **10**, 1411 (2020)

- 15. F. Liu, R. Zhang, B.H. DeProspo, S. Dwarakanath, P. Nimbalkar, S. Ravichandran, D. Weyers, M. Kathaperumal, R.R. Tummala, M. Swaminathan, *2020 IEEE 70th Electronic Components and Technology Conference (ECTC)* (Orlando, June 3–30, 2020), pp. 1132–1139

- 16. R. Zhang, F. Liu, M. Kathaperumal, M. Swaminathan, R.R. Tummala, *IEEE Trans. Compon. Packaging Manuf. Technol.* **10**, 393 (2020)

- 17. P. Nimbalkar, F. Liu, A. Watanabe, D. Weyers, M. Kathaperumal, C.-P. Lin, F. Naohito, T. Makita, N. Watanabe, A. Kubo, M. Swaminathan, R. Tummala, *2020 IEEE 70th Electronic Components and Technology Conference (ECTC)* (Orlando, June 3–30, 2020), pp. 62–67

- 18. K. Radhakrishnan, M. Swaminathan, B. Bhattacharyya, *IEEE Trans. Compon. Packaging Manuf. Technol.* **11**, 655 (2021)

- 19. G. Ouyang, X. Chen, Y. Liang, C. Macziewski, J. Cui, *J. Magn. Magn. Mater.* **481**, 234 (2019)

- 20. C.Ó. Mathúna, et al., in IEEE Transactions on Power Electronics (2012)

- 21. Y.-W. Zhao, X.K. Zhang, J.Q. Xiao, *Adv. Mater.* 17, 915 (2005)

- 22. S. Ge, D. Yao, M. Yamaguchi, X. Yang, H. Zuo, T. Ishii, D. Zhou, F. Li, *J. Phys. D. Appl. Phys.* **40**(12), 3660 (2007)

- 23. M. Yamaguchi, et al., J. Appl. Phys. (1999)

- 24. M. Yamaguchi, et al., J. Magn. Magn. Mater. (2000)

- 25. D.S. Gardner, G. Schrom, F. Paillet, B. Jamieson, T. Karnik, S. Borkar, *IEEE Trans. Magn.* **45**(10), 4760 (2009)

- 26. W. Günther, P. Winkler, A user guide to soft magnetic materials, PhD dissertation, Georgia Institute of Technology (2018)

- 27. M.L.F. Bellaredj, A.K. Davis, P. Kohl, M. Swaminathan, *IEEE J. Emerg. Selected Topics in Power Electron.* (2019)

- 28. C. Alvarez, S. Suresh, M. Swaminathan, R. Tummala, D. Sasaki, K. Watanabe, R. Nagatsuka, C.P. Lin, T. Wada, N. Watanabe, *2020 IEEE 70th Electronic Components and Technology Conference (ECTC)* (Orlando, June 3–30, 2020), pp. 405–413

- 29. Ultra-Small Case Size Passive Electronic Components, 502 Ballad Creek Court, Cary NC, 27519 USA

- 30. Oak-Mitsui, Reduce EMI and Improve Power Delivery with Embedded Capacitance (2014)

- 31. J. Savic, R.T. Croswell, A. Tungare, G. Dunn, T. Tang, R. Lempkowski, M. Zhang, T. Lee, *CircuiTree*, (June), 10–24 (2002)

- 32. 3M. PCB West. 2011.

- 33. P. Nanni, V. Massimo, V. Buscaglia, Synthesis of Dielectric Ceramic Material, Handbook of Low and High Dielectric Constant Materials and Their Applications (Elsevier,

- 34. S.P. Consulting, TSMC Deep Trench Capacitor: Reverse Costing Analysis (2016) 35. B. Summey, in APEC (2017)

- 36. R. Spurney et al., J. Electron. Mater. (2019)

- 37. K. Yoshida, H. Saita, T. Kariya, 2020 IEEE 70th Electronic Components and Technology Conference (ECTC) (Orlando, June 3-30, 2020), pp. 414-418

- 38. Y. Min, R. Olmedo, M. Hill, K. Radhakrishnan, K. Aygun, M. Kabiri-Badr, R. Panat, S. Dattaguru, H. Balkan, 2013 IEEE 63rd Electronic Components and Technology Conference (ECTC) (Las Vegas, May 28-31, 2013), pp. 1225-1229

- 39. R. Phraser, C. Chiu, Materials for Advanced Packaging (Springer, Geneva, Switzerland, 2016)

- 40. K. Sebnem, O. Guralp, A. Ayse, Thermochim. Acta 499, 40 (2010)

- 41. B.Z. Gao, J.Z. Xu, J.J. Peng, F.Y. Kang, H.D. Du, J. Li, S.W. Chiang, C.J. Xu, N. Hu, X.S. Ning, Experimental and theoretical studies of effective thermal conductivity of composites made of silicone rubber and Al<sub>2</sub>O<sub>3</sub> particles. Thermochim. Acta 614, 1 (2015)

- 42. Z. Wenying, Q. Shuhua, T. Chunchao, Z. Hongzhen, W. Caifeng, K. Jingli, J. Appl. Polym. Sci. (2007)

- 43. D. Pal, Y.K. Joshi, in Proceedings of the Pacific Rim/ASE International Society Electronic & Photonic Packging Conference (American Society of Mechanical Engineers, New York, 1999), vol. 2, pp. 1625-1630

- 44. R. Clarksean, Y. Chen, M. Marongiu, in Proceedings of the Pacific Rim/ASME International Intersociety Electronic & Photonic Packaging Conference (American Society of Mechanical Engineers, New York, 1999), vol. 2, pp. 1611-1616

- 45. R. Clarksean, Y. Chen, in Proceedings of the Pacific Rim/ASME International Intersociety Electronic & Photonic Packaging Conference (American Society of Mechanical Engineers, New York, 1999), vol. 2, pp. 1631-1640

- 46. L. Qizhen, M. Kyoung-Sik, J. Hongjin, W. Ching Ping, in IEEE TCPMT (2012)

- 47. Z. Rongwei, M. Kyoung-sik, L. Wei, W. Ching Pong, J. Mater. Chem. (2010)

- 48. K. Pashayi, H.R. Fard, F. Lai, S. Iruvanti, J. Plawsky, T. Borca-Tasciuc, J. Appl. Phys. **111**. 104310 (2012)

- 49. Z. Xiaoliang, Y. Yimin, G. Zhengyu, W. Fangfang, S. Rong, X. Jianbin, W. Ching-Ping, in Polymer Composites for Thermal Conductivity Improvement (2015)

- 50. N. Yang, X. Zeng, J. Lu, R. Sun, C.-P. Wong, Appl. Phys. Lett. (2018)

- 51. L. Ren, X. Zeng, R. Sun, J.-B. Xu, C.-P. Wong, Chem. Eng. J. (1996)

- 52. T. Zhang, J. Sun, L. Ren, Y. Yao, M. Wang, X. Zeng, R. Sun, J.-B. Xu, C.-P. Wong, Compos Part A Appl. Sci. Manuf. (2019)

- 53. Z. Lin, A. McNamara, Y. Liu, K-s. Moon, C.P. Wong, Compos. Sci. Technol. 90, 123

- 54. Z. Lin, Y. Liu, S. Raghavan, K-s. Moon, S.K. Sitaraman, C.P. Wong, ACS Appl. Mater. Interfaces 5(15), 7633 (2013)

- 55. L. Ziyin, Y. Yagang, M. Andrew, M. Kyoung-sik, W. C. P, in IEEE (2012)

- 56. Y. Yao, Z. Lin, Z. Li, X. Song, K.-S. Moon, C P. Wong, J. Mater. Chem. (2012)

- 57. S. William Anderson Lee, H. Chen-Yang, C. Jian-Xun, S. Yu-Chian, C. Ying-Nan, C. Kuo-Chan, L. Tzong-Ming, C. Chih-Chia, C. Chih-Wei, Polymers (2021)

- 58. F. Jiang, N. Song, R. Ouyang, P. Ding, ACS Appl. Mater. Interfaces (2021)

- 59. G. Han, X. Zhao, Y. Feng, J. Ma, K. Zhou, Y. Shi, C. Liu, X. Xie, Chem. Eng. J. (2021)

- 60. D. An, S. Cheng, C. Jiang, X. Duan, B. Yang, Z. Zhang, J. Li, Y. Liu, C.-P. Wong, J. Mater. Chem. C (2020)

- 61. J. Hu, Y. Huang, Y. Yao, G. Pan, J. Sun, X. Zeng, R. Sun, J.-B. Xu, B. Song, C.-P. Wong, ACS Appl. Mater. Interfaces (2017)

- 62. F. Wang, X. Zeng, Y. Yao, R. Sun, J. Xu, C.-P. Wong, Sci. Rep. (2016)

- 63. R. Collins, J. Edmondson, Thermal Interface Materials 2020–2030, Forecasts, Technologies, Opportunities Market trends and drivers for key industries; technology trends and emerging material opportunities.

- 64. L. Wei, S. Jintang, G. Wentian, W. C.P. Carbon (2012)

- 65. J. Tengxiao, F. Yiyu, Q. Mengmeng, F. Wei, Compos. Part A (2016)

- 66. L. Qizhen, Y. Xuxia, W. Wei, L. Yan, W. Ching Ping, ACS Nano (2011)

- 67. Z. Xing, W. Sun, L. Wang, Z. Yang, S. Wang, G. Liu, J. Mater. Sci. (2019)

- 68. J. P. Song, K. Y. Tian, L. X. Ma, W. Li, S. C. Yao, Int. J. Heat Mass Transfer (2019)

- 69. T. Kessel, IBM Research Report, IBM

- 70. L. Zhao, H. Liu, X. Chen, S. Chu, H. Liu, Z. Lin, Q. Li, G. Chu, H. Zhang, Electronic supplementary information (ESI) (2018). https://doi.org/10.1039/c8tc03417f

- 71. M. T. Barako, ., S.G. Isaacson, F. Lian, .E. D. Pop, H. Reinhold K. E. Goodson, J. Tice, ACS Appl. Mater. Interfaces (2017)

- 72. W. Shouling, C. Yin, W. Ranran, S. Jing, G. Lian, ACS Appl. Mater. Interfaces (2014) 6481

- 73. A. P., S. S., M. D., Z. T., L. D., Microelectron. J. (2014)

- 74. P. Binghua, Y. Chee Keng, SAE Int. J. Mater. Manuf. (2014)

- 75. Y. Bao, Y. Bao, A. Wu, A. Wu, H. Shao, H. Shao, Y. Zhao, Y. Zhao, L. Liu, L. Liu, G. Zou, G. Zou, J. Mater. Sci. (2019)

- 76. Y. Chi-Tung, Q. Wei-Chun, J. Jiao-Dong, P. Ji-An, L. Rong-Zheng, N. Gong-Dun, L. Chang-Fu, C. Key, in IEEE Thermal Interface Materials 2020–2030: Forecasts, Technologies, Opportunities Market trends and drivers for key industries (2016)

- 77. S. Dwarakanath, "Ultra-Low Dielectric Constant and Ultra-Thin Polymer Dielectric Materials, Processes and Reliability for Ultra-High Bandwidth Computing Applications," PhD thesis, Georgia Institute of Technology (2020) П

Madhavan Swaminathan is the John Pippin Chair in Microsystems Packaging & Electromagnetics in the School of Electrical and Computer Engineering (ECE), professor in ECE with a joint appointment in the School of Materials Science and Engineering (MSE), and director of the 3D Systems Packaging Research Center (PRC), Georgia Tech (GT) (http://www.prc.gatech.edu). He also serves as the site director for the National Science Foundation Center for Advanced Electronics through Machine Learning (CAEML: https://www.publish.illinois.edu/advan cedelectronics/) and theme leader for Heterogeneous Integration at the SRC JUMP ASCENT Center (https://ascent.nd.edu/). Prior to joining

GT, Swaminathan was with IBM Corporation working on packaging for supercomputers. He received his MS and PhD degrees in electrical engineering from Syracuse University in 1989 and 1991, respectively. He is the author of 530+ refereed technical publications and holds 31 patents. He is the primary author and co-editor of three books and five book chapters, founder and co-founder of two start-up companies, and founder of the IEEE Conference on Electrical Design of Advanced Packaging and Systems (EDAPS), a premier conference sponsored by the IEEE Electronics Packaging Society (EPS). Swaminathan is an IEEE Fellow and has served as the Distinguished Lecturer for the IEEE Electromagnetic Compatibility (EMC) society.

Mohan Kathaperumal is a senior research engineer/instructor at the 3D Systems Packaging Research Center (PRC) and School of Electrical and Computer Engineering at Georgia Institute of Technology since 2019. He received his PhD degree in chemistry from the Indian Institute of Science, Bangalore, He had earlier held research positions at universities and worked at Nitto Denko Technical Corporation as a chief researcher/associate director, developing electro-optic, photorefractive, and high-k materials. His current research interests include advanced materials and processes for packaging/heterogeneous integration targeting applications in Al/ HPC5G and beyond, energy storage, and optoe-

lectronics. Kathaperumal can be reached by email at kmohan@ece.gatech.edu.

Kyoung-sik Moon is a staff engineer at 3D Systems Packaging Research Center, Georgia Institute of Technology. He received his PhD degree in the Department of Materials Science and Engineering from Korea University, Seoul, South Korea, in 1999 and had worked in the School of Materials Science and Engineering at the Georgia Institute of Technology, as a postdoc and research engineer. His current research interests include advanced materials and assembly/process for packaging and energy storage devices with a focus on heterogeneous integration targeting applications. Moon can be reached by email at Jack.moon@gatech.edu.

Himani Sharma is a lecturer in School of Materials Science and Engineering (MSE) at the Georgia Institute of Technology (GT) since 2018. Prior to her teaching engagement at GT, she served for 10 years as a research scientist-II in the Packaging Research Center (PRC) at GT. Sharma received her PhD degree in chemistry from the University of Delhi, India, and later joined Alabama A&M University as a postdoctoral fellow. Her research focused on developing materials for next-generation electronics and packaging. More recently in addition to teaching undergrads, she has been developing passive component technologies focused on improved properties, miniaturization, and cost. Sharma

can be reached by email at himani.sharma@mse.gatech.edu.

Prahalad Murali received his BTech degree in metallurgical and materials engineering from the National Institute of Technology, Tiruchirappalli, India in 2019. He is currently pursuing his PhD degree in materials science and engineering at the 3D Systems Packaging Research Center, Georgia Institute of Technology. His current research interests include fabrication of package-embedded inductors and synthesis of magnetic materials for DC-DC converters. Murali can be reached by email at prahalad. murali@aatech.edu.

Siddharth Ravichandran received his bachelor's degree in electrical engineering from the College of Engineering, Guindy, India, in 2013, master's degree in electrical and computer engineering from Rutgers University, in 2016, and PhD degree in electrical engineering from Georgia Institute of Technology in 2021. During his PhD degree, he worked with the 3D Systems Packaging Research Center to develop advanced glass packages for RF, mm-wave, and high-performance computing (HPC) applications. Ravichandran received the 2020 IEEE Electronics Packaging Society (EPS) PhD Fellowship Award for his contributions to the development of 2.5D and 3D glass packages for hetero-

geneous integration in HPC. He also received the 2019 IEEE EPS "Future Packaging Vision" Award at the 69th Electronics Components and Technology Conference. His current research interests include heterogenous integration, 2.5D/3D architectures, power delivery, and advanced packaging for HPC applications.